新しい64 Gbaud BERTソリューションがテストセットアップの簡素化と400Gレシーバーのテストの高速化を実現

2017/09/06

キーサイト・テクノロジー株式会社

~業界で最も機能が統合されているPAM-4/NRZ向けビット・エラー・レシオ・テスター(BERT)に、新たな調整可能イコライザーを搭載~

■パターンジェネレーターが一体化し、レシーバーテストのセットアップを簡素化

■内蔵イコライザーの使用により、閉じたアイパターンを再度開き、再現性の高い結果を提供

■将来的なニーズに合わせ、拡張とアップグレードが可能

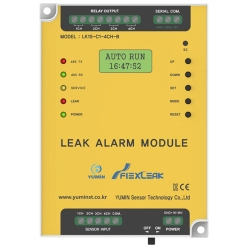

東京、2017年9月6日発 – キーサイト・テクノロジー合同会社(職務執行者社長:チエ ジュン、本社:東京都八王子市高倉町9番1号)は、最大動作速度64 GbaudのPAM-4およびNRZ方式に対応したM8040A高性能ビット・エラー・レシオ・テスター(BERT)ソリューションの機能拡張を発表しました。最新の400Gデータセンター・インターコネクト向けレシーバーの物理層での特性を評価するテストラボや研究開発のエンジニアは、テストセットアップの簡素化および再現性が高く正確な試験が可能になります。

現在のデータセンターのインフラは、帯域幅の増加、消費電力、距離、サービスの差別化に対応するための最適化が継続的に行われています。伝送レートの向上、伝送ライン数の増加、PAM-4などの新しいマルチレベル・データ・フォーマットを採用することで、次世代データセンターに必要な伝送帯域幅の需要に対応しています

最新のIEEE 802.3bsおよびOIF CEI-56Gの実装協定では、最大400Gb/sの通信を実現するためのチップ間、チップ-モジュール間、バックプレーンのような電気インタフェースから光インタフェースまでをPAM-4やNRZで規定しています。研究開発およびテストラボでは、PAM-4やNRZで最大64 Gbaudのデータレートでデータセンター向けレシーバー特性を評価する必要があり、タイミングマージンの縮小、チャネル損失、非直線性、レベル干渉、クロストークの影響など、新しいテスト課題を抱えており、テストの効率化と精度が重要になっています。

チップ間やチップ-モジュール間、バックプレーンなどの電気インタフェースでチャネル損失を克服するのは、シンボルレートの高速化にとって大きな課題です。ディエンファシスなどのプリディストーション技法は、レシーバーのトランスミッタとイコライザーで使用され、シンボル間干渉によって閉じたアイパターンを再度開くために役立ちます。

キーサイトのネットワーク・データセンターソリューションビジネス部門バイスプレジデント兼統括マネージャーであるJoachim Peerlingsは次のように述べています。「M8040AはPAM-4信号とNRZ信号のテスト用に一体化したレシーバー・テスト・ソリューションです。新たに内蔵されたイコライゼーション機能によって、レシーバーテストはさらに効率化され、お客様がソリューションを市場投入するまでの時間を短縮できます。M8040Aにより、研究開発やテストに携わるエンジニアは、400Gデータセンター・インターコネクトのレシーバーテストの課題を克服できます。」

M8040Aは、AXIeモジュール型のM8000シリーズBERテストソリューションの最新機種です。最大64 GbaudのPAM-4信号と最大64Gbit/sのNRZ信号に対応する一体型のBERTです。パターンジェネレーターモジュールには、内蔵ディエンファシス機能、ジッタ注入機能、第2チャネルを実装することができます。エンジニアと設計者は、PAM-4とNRZをユーザーインタフェース上で選択するだけで切り替えることができ、PAM-4信号のための外部コンバイナー、配線、スキュー補正が不要となります。信号品質を高めるために、リモートヘッドを被測定デバイスの近くに配置できます。アナライザモジュールは、PRBSおよびQPRBSの長いパターンに対して、リアルタイムで真のPAM-4エラー解析を実行でき、要求される信頼度で、低いビット・エラー・レシオとシンボル・エラー・レシオを証明できます。

エラーアナライザは、NRZ信号について最大64 G baudのシンボルレートと内蔵された調整可能なイコライゼーション機能に対応するようになりました。ユーザーはグラフィックのリモートコントロールインタフェースからM8040Aを制御できます。

■パターンジェネレーターが一体化し、レシーバーテストのセットアップを簡素化

■内蔵イコライザーの使用により、閉じたアイパターンを再度開き、再現性の高い結果を提供

■将来的なニーズに合わせ、拡張とアップグレードが可能

東京、2017年9月6日発 – キーサイト・テクノロジー合同会社(職務執行者社長:チエ ジュン、本社:東京都八王子市高倉町9番1号)は、最大動作速度64 GbaudのPAM-4およびNRZ方式に対応したM8040A高性能ビット・エラー・レシオ・テスター(BERT)ソリューションの機能拡張を発表しました。最新の400Gデータセンター・インターコネクト向けレシーバーの物理層での特性を評価するテストラボや研究開発のエンジニアは、テストセットアップの簡素化および再現性が高く正確な試験が可能になります。

現在のデータセンターのインフラは、帯域幅の増加、消費電力、距離、サービスの差別化に対応するための最適化が継続的に行われています。伝送レートの向上、伝送ライン数の増加、PAM-4などの新しいマルチレベル・データ・フォーマットを採用することで、次世代データセンターに必要な伝送帯域幅の需要に対応しています

最新のIEEE 802.3bsおよびOIF CEI-56Gの実装協定では、最大400Gb/sの通信を実現するためのチップ間、チップ-モジュール間、バックプレーンのような電気インタフェースから光インタフェースまでをPAM-4やNRZで規定しています。研究開発およびテストラボでは、PAM-4やNRZで最大64 Gbaudのデータレートでデータセンター向けレシーバー特性を評価する必要があり、タイミングマージンの縮小、チャネル損失、非直線性、レベル干渉、クロストークの影響など、新しいテスト課題を抱えており、テストの効率化と精度が重要になっています。

チップ間やチップ-モジュール間、バックプレーンなどの電気インタフェースでチャネル損失を克服するのは、シンボルレートの高速化にとって大きな課題です。ディエンファシスなどのプリディストーション技法は、レシーバーのトランスミッタとイコライザーで使用され、シンボル間干渉によって閉じたアイパターンを再度開くために役立ちます。

キーサイトのネットワーク・データセンターソリューションビジネス部門バイスプレジデント兼統括マネージャーであるJoachim Peerlingsは次のように述べています。「M8040AはPAM-4信号とNRZ信号のテスト用に一体化したレシーバー・テスト・ソリューションです。新たに内蔵されたイコライゼーション機能によって、レシーバーテストはさらに効率化され、お客様がソリューションを市場投入するまでの時間を短縮できます。M8040Aにより、研究開発やテストに携わるエンジニアは、400Gデータセンター・インターコネクトのレシーバーテストの課題を克服できます。」

M8040Aは、AXIeモジュール型のM8000シリーズBERテストソリューションの最新機種です。最大64 GbaudのPAM-4信号と最大64Gbit/sのNRZ信号に対応する一体型のBERTです。パターンジェネレーターモジュールには、内蔵ディエンファシス機能、ジッタ注入機能、第2チャネルを実装することができます。エンジニアと設計者は、PAM-4とNRZをユーザーインタフェース上で選択するだけで切り替えることができ、PAM-4信号のための外部コンバイナー、配線、スキュー補正が不要となります。信号品質を高めるために、リモートヘッドを被測定デバイスの近くに配置できます。アナライザモジュールは、PRBSおよびQPRBSの長いパターンに対して、リアルタイムで真のPAM-4エラー解析を実行でき、要求される信頼度で、低いビット・エラー・レシオとシンボル・エラー・レシオを証明できます。

エラーアナライザは、NRZ信号について最大64 G baudのシンボルレートと内蔵された調整可能なイコライゼーション機能に対応するようになりました。ユーザーはグラフィックのリモートコントロールインタフェースからM8040Aを制御できます。